Questa Equivalence FPGA garantit que les optimisations avancées nécessaires pour atteindre des objectifs ambitieux

en termes de consommation, de performances et de surface n’altèrent en rien l’intégrité fonctionnelle du design

En prenant en charge des fonctionnalités clés telles que l’inférence de RAM/ROM fixes ou distribuées, l’optimisation des DSP, le recoding des machines à états finis (FSM) et le register retiming, la solution accélère les phases de vérification. Elle réduit le recours aux simulations gate-level et permet d’identifier rapidement des anomalies souvent difficiles à détecter dans le flux d’implémentation.

Le support personnalisé des outils des fournisseurs FPGA, associé à des optimisations spécifiques aux dispositifs, offre une précision inégalée dans la détection des écarts de conception. Cette approche garantit que le design se comporte exactement comme prévu à chaque étape de la synthèse et du place-and-route (P&R).

Fonctionnalités, performances et coûts améliorés

Questa Equivalence FPGA élève le niveau de qualité des designs FPGA en s’appuyant sur des méthodes de vérification avancées, parfaitement adaptées aux architectures FPGA modernes. La solution réduit les temps de vérification et garantit la conformité fonctionnelle du design, même après des optimisations complexes de synthèse et de place-and-route (P&R).

Vérification RTL complète sur l'ensemble de l'exécution du FPGA

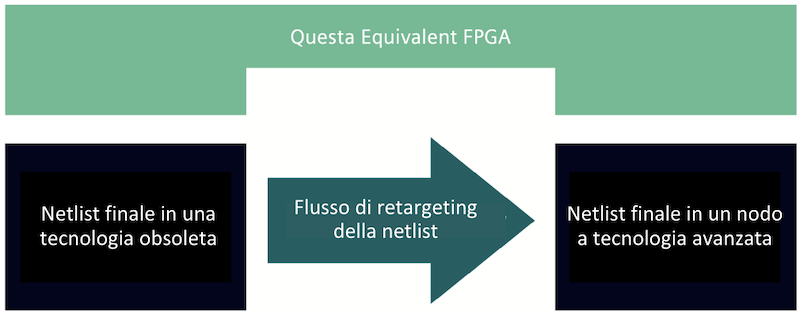

Questa Equivalence FPGA assure l’équivalence entre le RTL et la netlist finale en combinant des moteurs de preuve combinatoires et séquentiels puissants. Il répond aux défis spécifiques du FPGA, tels que l’insertion de registres de pipeline ou le recoding des machines à états finis (FSM), tout en maintenant une cohérence stricte de l’implémentation.

Détection et débogage des erreurs plus rapides

La solution permet de valider rapidement les flux d’optimisation FPGA de dernière génération et d’identifier précisément l’origine des écarts d’implémentation. Les cycles de débogage sont considérablement réduits, ce qui accélère le processus de conception et limite le recours aux simulations gate-level.

Intégration avec des outils spécifiques aux fournisseurs

Questa Equivalence FPGA s’intègre directement aux outils leaders du marché, notamment AMD-Xilinx Vivado, Intel Quartus et Microchip Libero. Cette intégration garantit une configuration fluide et une vérification simplifiée, grâce à la génération automatique de scripts et à un mapping transparent vers la technologie FPGA cible.

En savoir plus sur le contrôle d'équivalence avec Questa Equivalent FPGA

Vérification avancée de l’implémentation FPGA

Démonstrateurs combinés et séquentiels

Détection rapide des erreurs et débogage ciblé

Support pour optimisation spécifique

Réduction drastique des simulations gate-level