Questa Equivalence Check for FPGA ensures that the advanced optimizations required to achieve ambitious power, performance, and area goals do not alter the functional integrity of the design.

Supporting features such as fixed and distributed RAM/ROM inference, DSP optimization, finite state machine (FSM) recoding, and register retiming, it accelerates verification by reducing the need for gate-level simulations and by quickly identifying hard-to-detect issues within the implementation flow.

Customized FPGA vendor tool support and device-specific optimizations provide unparalleled accuracy in detecting design discrepancies, ensuring that the design performs as intended at every stage of synthesis and place-and-route (P&R).

Improved functionality, performance and cost

Questa Equivalent FPGA improves the quality of FPGA designs by enabling advanced verification methods for modern FPGA architectures. It helps reduce verification time and ensure functional correctness even after complex synthesis and P&R optimizations.

Full RTL check on the entire FPGA execution

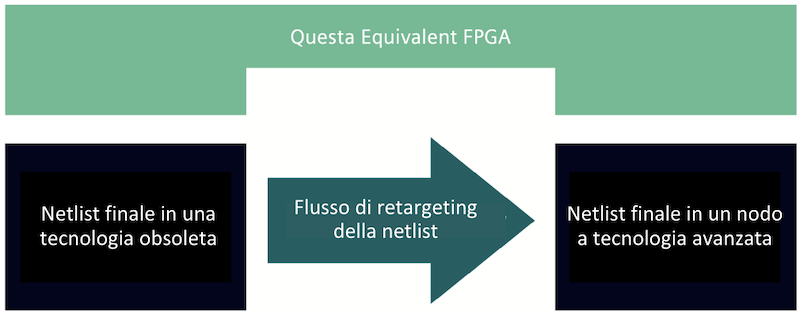

Questa Equivalent FPGA ensures equivalence from RTL to final netlist by combining powerful combinational and sequential provers. It addresses FPGA-specific challenges, such as pipelining registers and recoding FSMs, while ensuring implementation consistency.

Faster error detection and debugging

With Questa Equivalent FPGA, you can quickly verify modern FPGA optimization flows and pinpoint the exact source of implementation errors, significantly reducing debugging cycles. This speeds up the design process and minimizes gate-level simulations.

Integration with vendor-specific tools

Questa Equivalent FPGA integrates directly with leading FPGA vendor tools, including AMD-Xilinx Vivado, Intel Quartus, and Microchip Libero, ensuring a smooth configuration and verification process with automatic script generation and seamless mapping to the chosen FPGA technology.

Want to learn more about HDL simulation with Questa Base?

Advanced verification of FPGA implementation

Combinational and sequential demonstrators

Rapid error detection and debugging

Support for specific optimization

Minimized gate-level simulation