HDL Designer est un environnement HDL puissant utilisé par des ingénieurs et des équipes de conception du monde entier pour analyser, créer et gérer des conceptions FPGA et ASIC complexes

HDL Designer est un environnement HDL puissant utilisé par des ingénieurs et des équipes de conception du monde entier pour analyser, créer et gérer des conceptions FPGA et ASIC complexes

En combinant des capacités d’analyse avancées, des éditeurs de création performants et une gestion complète des designs et des flux de développement, HDL Designer offre un environnement de conception HDL qui accroît la productivité des concepteurs et des équipes, qu’elles soient locales ou internationales, tout en garantissant un processus de design reproductible, maîtrisé et prévisible.

Outils interactifs de visualisation et de création HDL

HDL Designer s’intègre dans une solution de conception complète dédiée au développement de FPGA et d’ASIC, que les équipes partent d’une feuille blanche ou évaluent des blocs RTL en vue de leur réutilisation. L’outil accompagne les équipes dans l’analyse, la création et la gestion de projets complexes, avec une vision globale et structurée du design.

Concevoir rapidement en utilisant des méthodes optimales

La conception de projets de grande envergure à partir d’IP ne se limite pas à l’écriture de code RTL. HDL Designer Series met à disposition une suite d’éditeurs de conception avancés pour accélérer le développement, tels que des tableurs de conception orientés interfaces et des outils d’édition de machines à états.

Évaluer rapidement la qualité du code nouveau et réutilisé

L’analyse du code est indissociable de sa création. HDL Designer aide les ingénieurs à maîtriser la complexité des designs RTL grâce à des analyses d’intégrité du code, de complétude des connectivités, d’évaluation de la qualité HDL et à des fonctionnalités avancées de visualisation des designs.

Gérer le code pendant le flux de développement

Au-delà de la création et de l’analyse, la gestion du design constitue un pilier essentiel du travail des concepteurs. En complément de la gestion des données de conception, les équipes doivent piloter le projet tout au long du flux. HDL Designer répond à cet enjeu en proposant des interfaces natives avec les autres outils de la chaîne de conception, intégrant des solutions de gestion des données et des versions pour un développement maîtrisé et traçable.

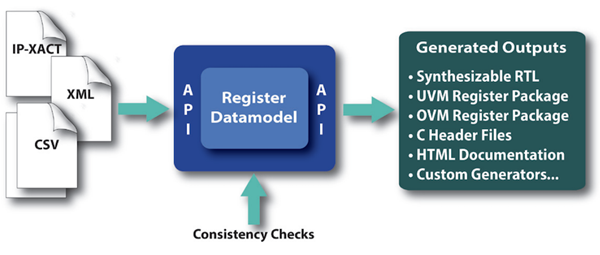

L'assistant de registre de HDL Designer automatise et simplifie la gestion des registres dans les flux de conception FPGA/ASIC, réduisant ainsi les erreurs et augmentant l'efficacité.

En savoir plus sur la conception et la gestion de codes HDL avancés avec HDL Designer?

avec HDL Designer

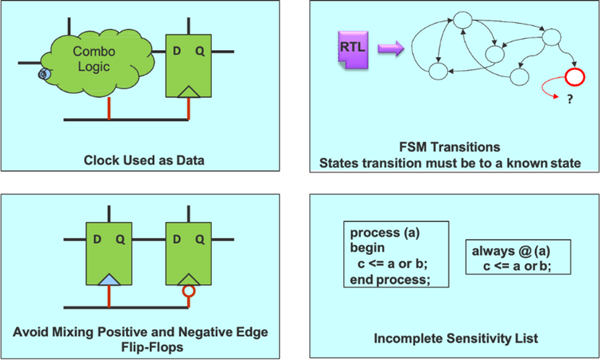

Le contrôle automatisé des règles de conception avec HDL Designer permet de réduire significativement les coûts de développement tout en améliorant la qualité du code HDL.

L’automatisation limite les efforts de relecture manuelle, accélère les phases de vérification du code HDL et identifie très en amont les défauts de conception, avant les étapes de simulation, de synthèse et de production, là où les corrections sont plus rapides et nettement moins coûteuses.

Le Design Checking, réalisable de manière interactive ou en mode batch, détecte les irrégularités d’implémentation des circuits grâce à un moteur de synthèse intégré. Il applique des contrôles sur l’ensemble du design, y compris à travers les frontières des modules, et impose des règles de style de codage garantissant lisibilité, réutilisabilité et cohérence du code.

Les 7 jeux de règles préconfigurés, dont le référentiel DO-254, offrent un cadre robuste de maîtrise du design. Les contrôles paramétrables permettent en parallèle de définir des jeux de règles et des politiques personnalisées, adaptées aux contraintes spécifiques de chaque projet. Les métriques de qualité et les résultats d’infractions sont consolidés dans des rapports de contrôle de conception, accélérant les revues de design. Chaque violation est directement reliée au code HDL et aux vues graphiques source, facilitant ainsi l’analyse et le débogage.