HDL Designer is a powerful HDL environment used by individual engineers and design teams worldwide to analyze, create, and manage complex FPGA and ASIC designs.

HDL Designer is a powerful HDL environment used by individual engineers and design teams worldwide to analyze, create, and manage complex FPGA and ASIC designs.

HDL Designer combines deep analysis capabilities with advanced authoring editors and comprehensive design and flow management to provide an HDL design environment that increases the productivity of designers and teams (local or remote), while also enabling a repeatable and predictable design process.

Interactive HDL visualization and creation tools

HDL Designer is part of a comprehensive design solution for the development of FPGAs and ASICs, whether a team is creating a design from scratch or evaluating RTL for reuse. The tool helps design teams analyze, create, and manage their complex projects.

Design quickly using optimal methods

Designing and creating large projects from IP efficiently requires more than just writing RTL. HDL Designer Series provides designers with a suite of advanced design editors to facilitate development: interface-based design spreadsheets and machine state editing.

Quickly assess the quality of new and reused code

Code analysis goes hand in hand with code creation. HDL Designer supports engineers in analyzing complex RTL designs by providing code integrity analysis, connectivity completeness analysis, HDL code quality assessments, and design visualization.

Manage code during the development flow

Together with design creation and analysis, design management is the third important task for designers. Along with design data management, teams must manage the project during the design flow. HDL Designer addresses the project management problem by providing the designer with interfaces to other design tools within the flow. Includes data and version management solutions.

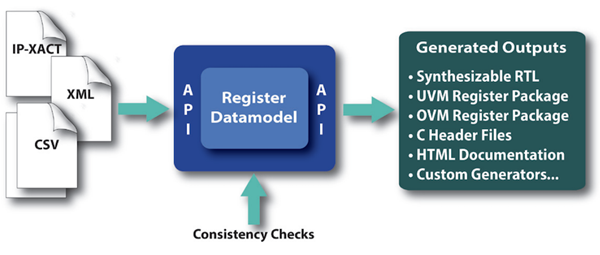

HDL Designer's Register Assistant automates and simplifies register management in FPGA/ASIC design flows, reducing errors and increasing efficiency.

Want to learn more about advanced HDL code design and management with HDL Designer?

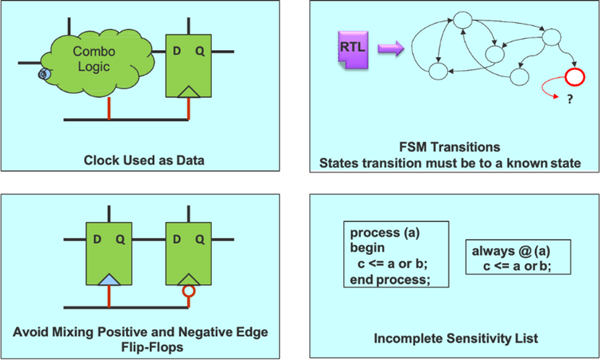

Automated design checking (Automated design checking) performed with HDL Designer reduces design costs and improves the quality of HDL code.

Automation decreases manual code review effort, speeds up HDL code checking, and identifies design flaws early in the development cycle before simulation, synthesis, and production, where è it is less costly and easier to correct violations.

Design Checking, which can be performed interactively or through batch processes, identifies irregularities in circuit implementation through a built-in synthesis engine, applies checks to the entire design to identify irregularities through module boundary crossings, and applies coding style rules for readability, reusability, and coding consistency.

The 7 preconfigured rule sets, including the DO-254 rule set, help control the design, while the parameterizable controls allow the creation of custom rule sets and policies. Quality metrics and infringement results are summarized in design control reports and expedite the design review process. Violations are linked to HDL code and source graphical views to support debugging.