HDL Designer es un potente entorno HDL utilizado por ingenieros individuales y equipos de diseño en todo el mundo para analizar, crear y gestionar diseños complejos de FPGA y ASIC.

HDL Designer es un potente entorno HDL utilizado por ingenieros individuales y equipos de diseño en todo el mundo para analizar, crear y gestionar diseños complejos de FPGA y ASIC.

HDL Designer combina capacidades de análisis profundo con editores de creación avanzados y una gestión integral del diseño y el flujo para proporcionar un entorno de diseño HDL que aumenta la productividad de los diseñadores y los equipos (locales o remotos), al tiempo que permite un proceso de diseño repetible y predecible.

Herramientas interactivas de visualización y creación de HDL

HDL Designer forma parte de una solución de diseño completa para el desarrollo de FPGAs y ASICs, tanto si un equipo está creando un diseño desde cero como evaluando RTL para su reutilización. La herramienta ayuda a los equipos de diseño a analizar, crear y gestionar sus proyectos complejos.

Diseñar rápido utilizando métodos óptimos

Diseñar y crear grandes proyectos a partir de IP de forma eficiente requiere algo más que escribir RTL. HDL Designer Series ofrece a los diseñadores un conjunto de editores de diseño avanzados para facilitar el desarrollo: hojas de cálculo de diseño basadas en interfaz y edición del estado de la máquina.

Evaluar rápidamente la calidad del código nuevo y reutilizado

El análisis de código va de la mano de la creación de código. HDL Designer ayuda a los ingenieros a analizar diseños RTL complejos proporcionándoles análisis de integridad de código, análisis de integridad de conectividad, evaluaciones de calidad de código HDL y visualización de diseño.

Gestiona el código durante el flujo de desarrollo

Junto con la creación de diseños y el análisis de diseños, la gestión de diseños es la tercera tarea importante para los diseñadores. Junto con la gestión de los datos de diseño, los equipos deben gestionar el proyecto durante el flujo de diseño. HDL Designer aborda el problema de la gestión de proyectos proporcionando al diseñador interfaces con otras herramientas de diseño dentro del flujo. Incluye soluciones de gestión de datos y versiones.

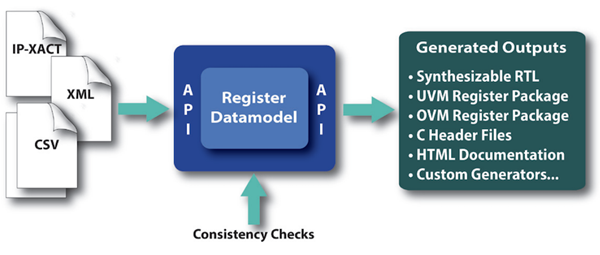

El asistente de registros de HDL Designer automatiza y simplifica la gestión de registros en los flujos de diseño de FPGA/ASIC, reduciendo errores y aumentando la eficiencia.

¿Deseas obtener más información sobre el diseño y la gestión avanzados de código HDL con HDL Designer?

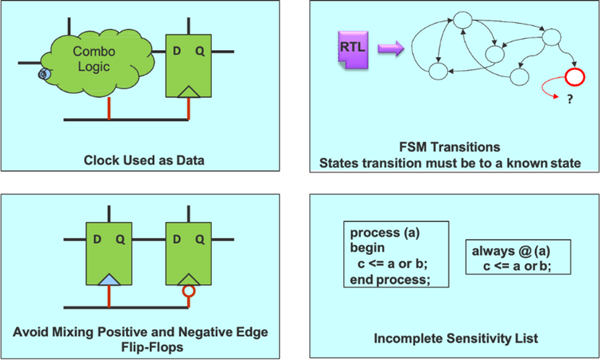

La verificación de diseño automatizada realizada con HDL Designer reduce los costos del proyecto y mejora la calidad del código HDL.

La automatización disminuye el esfuerzo de revisión manual del código, acelera la comprobación del código HDL e identifica los fallos de diseño en una fase temprana del ciclo de desarrollo, antes de la simulación, la síntesis y la producción, donde es más barato y fácil corregir las infracciones.

La verificación de diseño, que se puede realizar de forma interactiva o mediante procesos por lotes, identifica irregularidades en la implementación del circuito a través de un motor de síntesis integrado, aplica verificaciones durante todo el proyecto para identificar irregularidades en los cruces de límites de los módulos y aplica reglas de estilo de codificación para lograr legibilidad, reutilización y consistencia de la codificación.

Los 7 conjuntos de reglas preconfigurados, incluido el conjunto de reglas DO-254, ayudan a controlar el diseño, mientras que los controles parametrizables permiten crear conjuntos de reglas y políticas personalizados. Las métricas de calidad y los resultados de las infracciones se resumen en informes de control de diseño y agilizan el proceso de revisión del diseño. Las violaciones están vinculadas al código HDL y a las vistas gráficas del código fuente para respaldar la depuración.