Questa Inspect rileva automaticamente i bug più complessi nei progetti RTL, senza necessità di un testbench.

Questa Inspect rileva automaticamente i bug più complessi nei progetti RTL, senza necessità di un testbench.

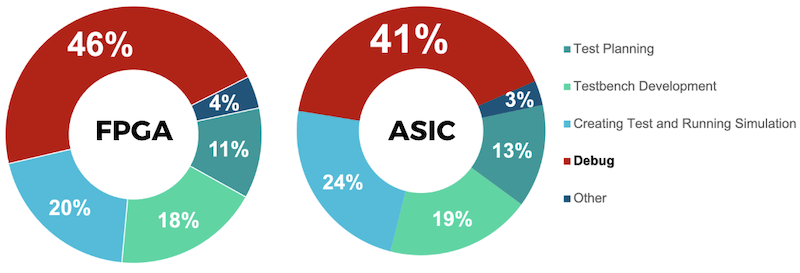

Con una verifica formale avanzata e la sintesi automatica delle asserzioni RTL, Questa Inspect identifica problemi sequenziali critici che la simulazione tradizionale potrebbe non rilevare. Grazie ai controlli automatici su inizializzazione, funzionalità e copertura, e a un'interfaccia intuitiva, si integra perfettamente nei flussi di sviluppo, migliorando l'accuratezza della verifica e semplificando il debugging.

Analisi sequenziale in profondità senza testbench

Questa Inspect esegue una verifica formale completa di problemi complessi di logica sequenziale, eliminando la necessità di creare testbench che richiedono molto tempo. Ciò accelera il processo di verifica e identifica i bug che i metodi tradizionali potrebbero trascurare.

Controlli formali automatizzati

Automatizza i principali controlli delle regole di progettazione FPGA, tra cui l'inizializzazione, i problemi funzionali e la raggiungibilità della copertura. Sintetizza in automatico i controlli in asserzioni, semplificando il processo di verifica e migliorando l'accuratezza.

Ambiente di debug facile da usare

Con finestre GUI dedicate al debug, Questa Inspect offre strumenti di debug strutturale mirati. I progettisti possono visualizzare i problemi in tempo reale con viste intuitive di schemi, forme d'onda e codice sorgente, garantendo una più rapida risoluzione dei problemi.

Integrazione in flussi di lavoro esistenti

Questa Inspect si integra facilmente con gli ambienti di progettazione RTL e i flussi di integrazione continua, supportando progetti ASIC e FPGA. Il supporto di linguaggi misti per Verilog, SystemVerilog e VHDL lo rende flessibile per vari processi di sviluppo.

Vuoi saperne di più sulla verifica formale automatizzata con Questa Inspect?

Analisi sequenziale

Verifiche formali automatizzate

Ambiente di debug focalizzato

Verifica con pulsante

Integrazione e usabilità