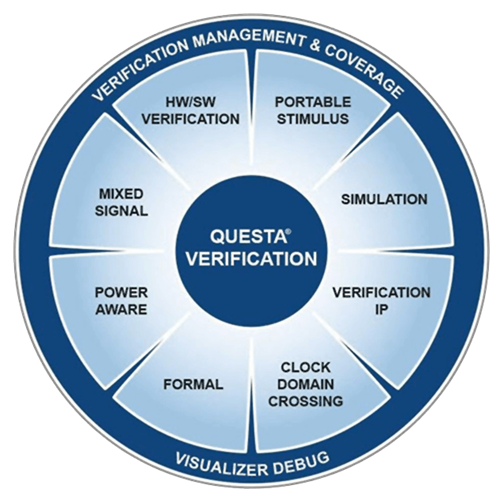

Questa Prime offers advanced, automated verification for complex designs, ensuring high quality and performance.

High Productivity

An extremely advanced verification solution that enables coverage closure for large and complex electronic systems.

Ease of Use

Ensures an intuitive user experience and rapid debugging through native assertions, offering a comprehensive debugging environment with multi-abstraction and multi-language capabilities, including transaction-level debugging.

Automated Test Development

Generates constrained-random stimuli to automate test creation and accelerate verification cycles.

Advanced Testbenches

Provides native advanced SystemVerilog testbench capabilities, combining OVM and UVM within a unified debugging environment to simplify the development and debugging of complex verification testbenches.

It continues to evolve in response to the growing complexity of SoC architectures.

Want to learn more about HDL simulation with Questa Base?

High performance and capability in FPGA design verification

Questa Prime’s advanced simulator for FPGA design verification delivers industry-leading performance and functionality.

Its exceptional performance and capabilities stem from powerful SystemVerilog and VHDL algorithms that boost SystemVerilog RTL simulation performance by up to ten times and enhance mixed VHDL/SystemVerilog simulations.

It also supports ultra-fast time-to-next simulation and efficient library management, ensuring consistently high performance.

The unique ability to pre-optimize and define block-level debugging visibility enables up to three times faster regression execution when running large test suites.

To further increase simulation performance for large projects with long runtimes, Questa Prime offers a Multi-Core option.

This feature leverages modern computing architectures by partitioning the design to run in parallel across multiple CPUs or machines, using both automatic and manual partitioning modes.

For even greater acceleration, Questa supports TBX, the highest-performing transaction-level link on the Veloce platform, enabling up to a 100× performance improvement with shared debug and testbench visibility.