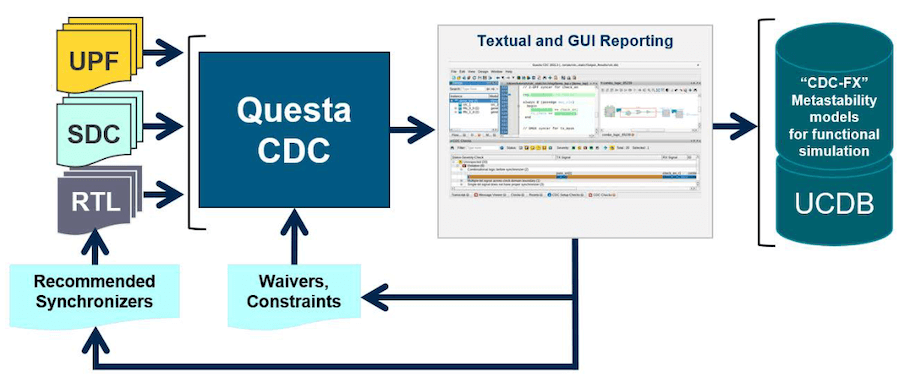

Questa CDC identifies and solves clock-domain traversal problems, ensuring reliable and scalable digital designs.

Using advanced structural analysis, Questa CDC discovers clock domains, synchronizers, and low-power structures, identifying timing and metastability issues early in the process. FPGA project. With comprehensive automated verification and debugging tools, it simplifies the validation process and integrates seamlessly into existing workflows. Ideal for complex large-scale projects, it ensures high quality, reliability, and significantly reduced risk of errors in production.

Exhaustive analysis of clock domain crossing

Questa CDC provides in-depth structural analysis to identify timing problems, metastability risks, and protocol violations in asynchronous clock domains. This avoids critical CDC problems that might be ignored by traditional simulation.

Automated and scalable verification

Questa CDC automates the CDC verification process, supporting SoC-level scalability for billion-gate designs. Its hierarchical approach and high-performance algorithms reduce setup time and provide faster and more accurate results.

Awareness of intent at low power

Questa CDC supports Unified Power Format (UPF) standards to ensure that low-power elements such as isolation cells, retention cells, and dynamic voltage scaling are verified correctly. This helps prevent CDC errors in low-power projects.

Total integration and easy setup

Thanks to Questa's direct integration and minimal configuration requirements, it offers immediate productivity. It automatically identifies clock domains and synchronizers, offering over 50 predefined synchronization styles and support for custom synchronizers.

Want to learn more about verifying clock domains with Questa CDC?

Automatic verification of Clock Domain Crossing (CDC)

Awareness of intent at low power

Scalable and high-performance analysis

Comprehensive debugging tools

This allows designers to easily identify CDC-related issues through a familiar, color-coded GUI and ensures they can quickly resolve clock domain crossing problems.

Full integration with Questa Simulation