.png?h=790&iar=0&w=1920&hash=0832792EF12EB6AD2C6D1D94860A1D4F)

Conception FPGA : simplicité et efficacité

Les solutions de conception FPGA sont reconnues pour leur capacité à combiner simplicité opérationnelle et efficacité de calcul, deux leviers clés pour optimiser le processus de conception et garantir des performances élevées.

Les FPGA sont conçus pour avoir une interface intuitive et ergonomique, permettant une configuration rapide et minimisant la complexité. De plus, l'approche de conception se concentre sur l'efficacité, en créant des architectures qui maximisent les performances tout en minimisant l'utilisation des ressources. Cela rend les FPGA à la fois simples à prendre en main et performants, parfaitement adaptés aux applications avancées et aux environnements d’ingénierie complexes.

Flux de conception FPGA Siemens EDA

Votre flux de conception FPGA est-il prêt à relever le défi des FPGA de nouvelle génération de plus en plus complexes ?

Êtes-vous confronté à des outils de travail qui ne sont pas intégrés les uns aux autres ?

Pouvez-vous obtenir la qualité de résultats escomptée avec le budget dont vous disposez ?

Vos équipes PCB et FPGA collaborent-elles pour définir les contraintes globales du système ?

Le flux de conception FPGA Siemens EDA est la réponse que vous attendiez.

Êtes-vous confronté à des outils de travail qui ne sont pas intégrés les uns aux autres ?

Pouvez-vous obtenir la qualité de résultats escomptée avec le budget dont vous disposez ?

Vos équipes PCB et FPGA collaborent-elles pour définir les contraintes globales du système ?

Le flux de conception FPGA Siemens EDA est la réponse que vous attendiez.

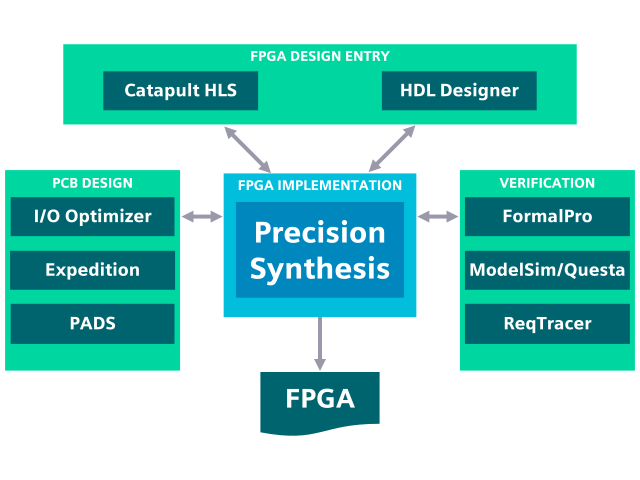

Flux complet de conception FPGA

Var Industries propose des solutions intégrées de conception FPGA basées sur la plateforme FPGA de Siemens. Celle-ci couvre l’ensemble du flux, de la saisie du design à la synthèse, en passant par la vérification, la vérification d’équivalence et la conception PCB, afin d’accélérer le développement des FPGA, de la phase de conception jusqu’à la carte finale, tout en répondant aux objectifs de qualité des résultats et aux exigences de contraintes système.

Intégration des outils

Pour accompagner chaque étape du flux de conception, Siemens EDA fournit une suite d'outils hautement spécialisés. Reqtracer assure une gestion complète de la traçabilité des exigences tout au long du cycle de développement, garantissant une cohérence totale entre les spécifications et leur implémentation. L'environnement graphique offert par HDL Designer fluidifie l'ingénierie de l'architecture RTL, tandis que Questa Lint et Questa Base réalisent des analyses statiques approfondies afin d'identifier en amont les erreurs, les écarts de style et les bugs potentiels. La simulation fonctionnelle s’appuie sur des outils de référence tels que ModelSim et Questa Prime, conçus pour accélérer le débogage et améliorer la couverture de vérification. Pour la vérification formelle et la détection de conditions critiques telles que les violations de synchronisation asynchrones, Questa Inspect et Questa CDC. Enfin, Questa Equivalence Check for FPGA permet de comparer et de vérifier l’équivalence entre les versions RTL et gate-level, garantissant la cohérence du design même après la phase de synthèse.

Logiciels pour la conception et la vérification FPGA

Afficher plus